事例紹介¶

リアルタイム認識¶

実装事例¶

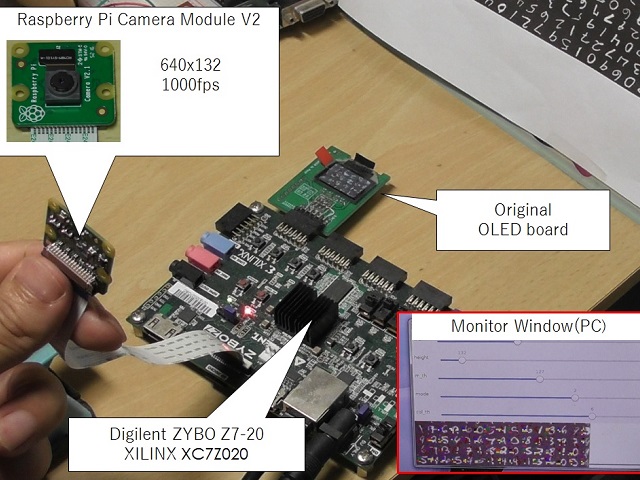

フルバイナリネットワークで、遅延数ミリ秒(1000fps)での画像認識の例です。

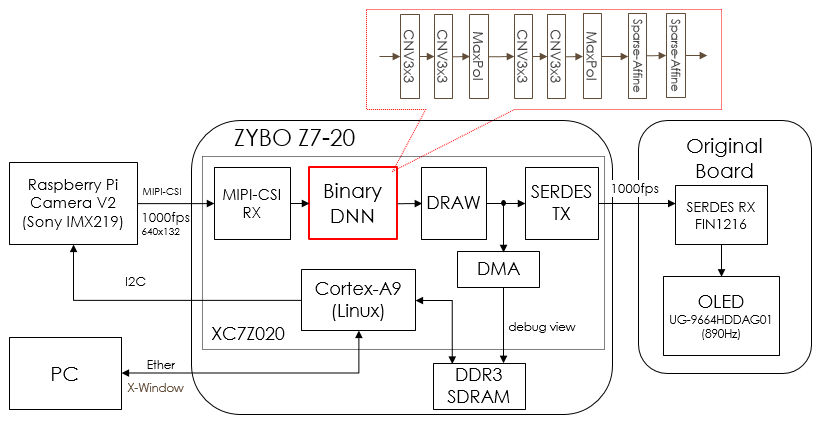

下記のようなブロック図となっています。

FPGAリソース¶

いくつかの認識について実験したものを以下に示します。

下記はカメラやOLEDなどの制御回路も含んだものもありますが、例えば MNIST の Simple DNN であればニューラルネット部分はわずか 1460個のLUTのみで88%の認識が可能です。 これは、今手に入るXILINXのもっとも小さなFPGAでも十分収まるサイズです。

これは 1024-360-60-10 の4層構造のネットワークであり、例えば200MHzで動かした場合、 4サイクル(=20ナノ秒)で認識が完了します。そのため極めてリアルタイム性の高い用途への応用も可能です。

もしカメラなどの入力に制約がなく、28x28の画像を毎サイクル供給可能であれば、 コア自体は 200Mfpsで動作可能となります。 これは1つの対象に対して条件を変えながら非常に多くの認識を行える帯域ですので、 1回の認識率は低くても、結果を二次加工することで実用的な認識率を目指すようなことも可能な帯域です。

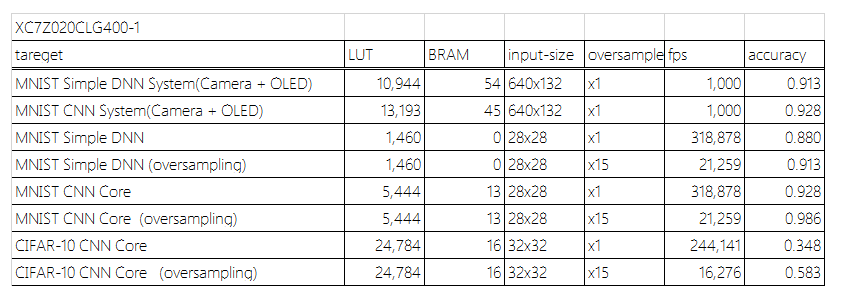

Autoencoder¶

通常のバイナリネットワークは出力もバイナリであるため、例えばAutoencoderのような 多値出力が必要な用途には応用が難しいという課題があります。 (入力に関しては最初の数層を多値で扱う手はあります)

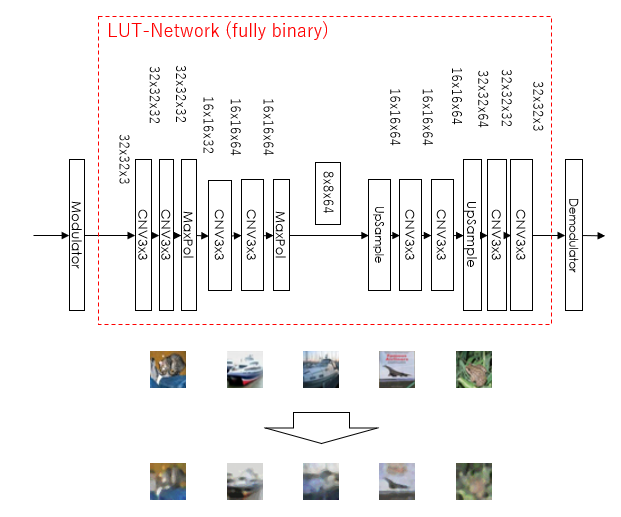

BinaryBrainでは、バイナリ変調を用いることで、入力から出力まで全層がバイナリである Fully binary neural network で多値データを扱う方法を提供しています。

MNIST¶

MNISTでの Autoencoder の実験結果です。

MNIST画像自体が2値に近いのですが、輪郭付近でやや滑らかさが出ています。

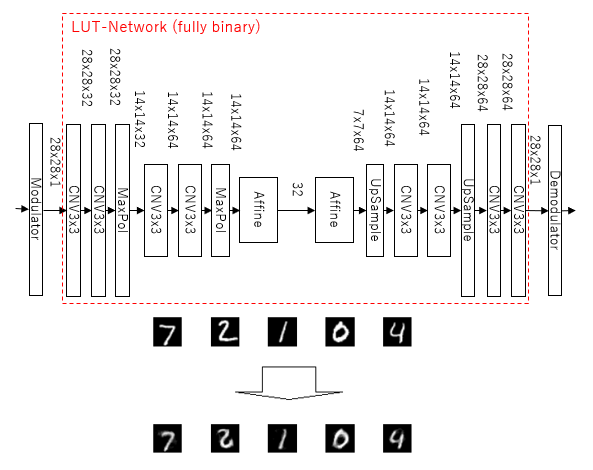

CIFAR-10¶

同様にCIFAR-10のデータセットで扱ったものです。

ぼやけた感じは否めませんが、多値出力に対してある程度のことができているのは確認できます。

もともとがCIFAR-10のデータセット自体が Autoencoder のような学習を目的としたデータセットではないので、 多値の従来ネットワークでもかなりボケた画像しか作れない部分はあるので、まずは実験的な結果と言えます。